TSMC 3nmプロセスによるHBM4 IPプラットフォームの実現

Global Unichip(GUC)は、TSMCの3nmプロセス技術を活用した12Gbps HBM4(High Bandwidth Memory 4)IPプラットフォームのデモンストレーションに成功したと発表しました。本プラットフォームは、GUCが独自に開発したフル機能のHBM4コントローラおよびPHY IPを、TSMCの先進パッケージング技術であるCoWoS(Chip on Wafer on Substrate)と統合したものです。

HBM4ではデータバス幅がHBM3Eと比較して2倍に拡張されており、さらなる処理能力の向上を実現しています。GUCの発表によれば、この新しいIPは帯域幅が2.5倍、電力効率が1.5倍、面積効率が2倍に向上しているとのことです。

Ms.ガジェット

Ms.ガジェット高度なモニタリングと3DICアーキテクチャへの対応

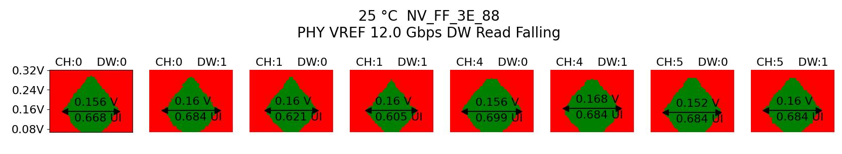

GUCのHBM4 IPには、proteanTecs社のインターコネクト・モニタリング・ソリューションが統合されています。これにより、PHYのテストや特性評価における可視性が高まり、最終製品の実稼働時におけるパフォーマンスと信頼性の向上が期待されています。

加えて、HBM4 PHYは「face-up」構成をサポートしており、TSMCの「SoIC(System on Integrated Chips)face-to-face」技術への統合が可能です。PHYマクロにはI/O信号や電源、Ground接続用のTSV(シリコン貫通電極)が統合されており、上層ロジック・ダイへの電力供給も考慮した設計となっています。

Ms.ガジェット

Ms.ガジェットGUC HBM4 IPの主な仕様と特徴

発表されたGUC HBM4 IPプラットフォームには、以下の技術的特徴が盛り込まれています。

- TSMC N3Pプロセスでの即時導入が可能(12Gbpsでのタイミング・サインオフ完了)

- 次世代のHBM4E(16Gbps対応)は2026年第2四半期に準備完了予定

- すべてのTSMC CoWoS技術(CoWoS-S、CoWoS-R、CoWoS-L)をサポート

- 高度な3D SoICアーキテクチャおよびface-up積層構成に対応

- インターポーザ配線においてAngle-Routing(任意の角度での柔軟な配線)をサポート

- proteanTecs社モニタリング技術によるチップレット間接続のリアルタイム監視

GUCは今回の発表にあわせ、UCIeやGLink-3D IPと組み合わせることで、最新の3.5Dシステムアーキテクチャに向けた包括的なIPソリューションを提供していく方針です。

Ms.ガジェット

Ms.ガジェット

GUC、3nmプロセス対応の12Gbps HBM4 IPプラットフォーム

最後までお読みいただきありがとうございました!

- 本記事の評価は当サイト独自のものです。

- 特段の表示が無い限り、商品の価格や情報などは記事執筆時点での情報です。

- この情報が誤っていても当サイトでは一切の責任を負いかねますのでご了承ください。

- 当サイトに記載された商品・サービス名は各社の商標です。

- 本記事で使用している画像は、メディアユーザーとしてPR TIMESより提供されたプレスリリース素材を利用しています。