組込みFPGA向け100Gbps RDMA IPのリリース

Intellectual Highway株式会社は、2025年12月22日、CPUレスでのストリーム入出力に対応した、FPGA用100Gbps RDMA (RoCEv2) IPをリリースしたと発表しました。

RDMA (Remote Direct Memory Access) は、CPUを介さずにネットワーク経由でメモリに直接アクセスする技術です。これにより、CPUの負荷を軽減し、高速かつ効率的なデータ転送が可能になります。

RDMA技術の活用分野

近年、AI学習用のデータセンターにおいて、高帯域・低遅延なメモリ転送が不可欠となっています。そのため、CPUパワーを消費せずにメモリ転送を行うRDMA技術が主流となっています。

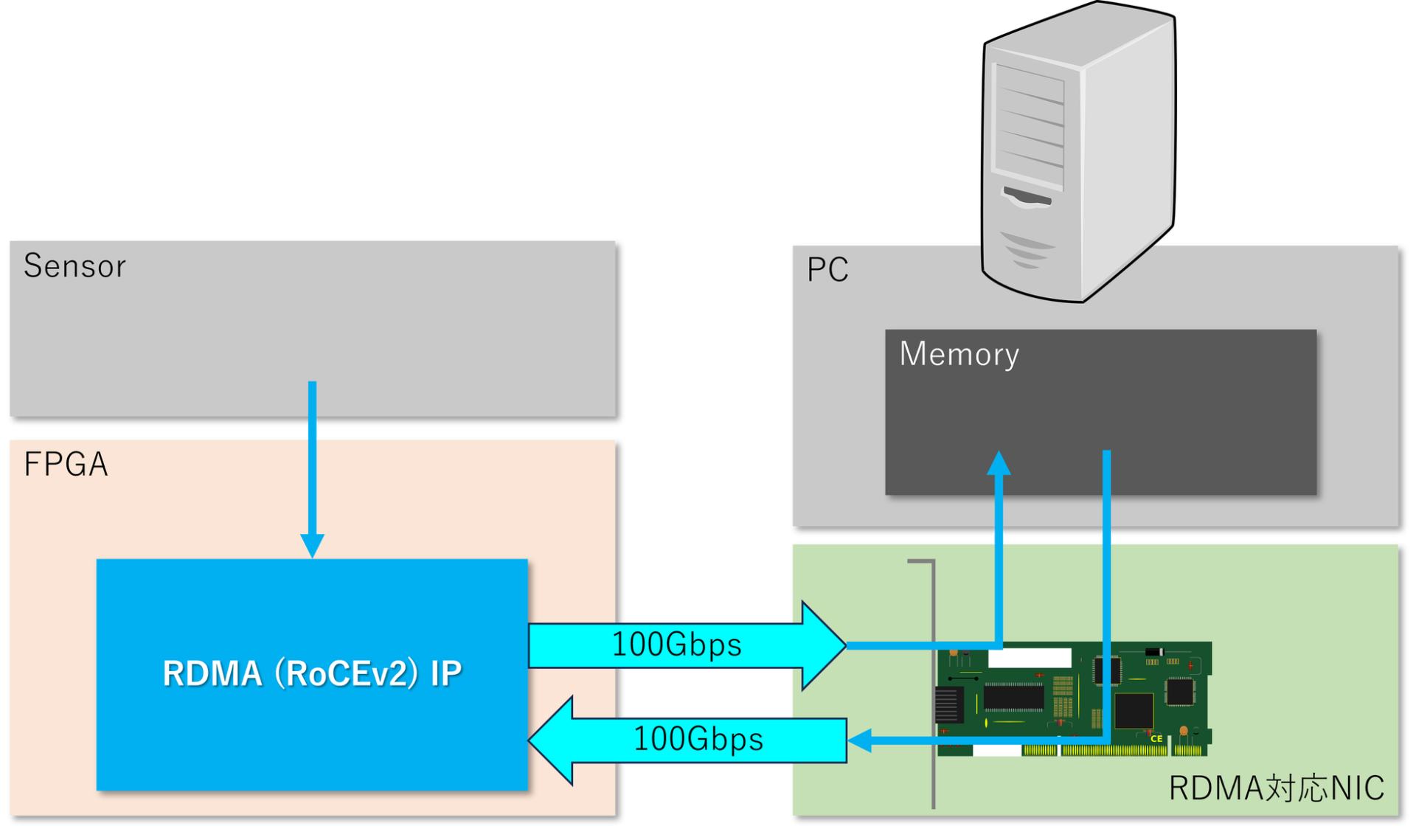

この技術は、半導体製造分野における高帯域なセンシングデータの伝送や、映像分野における非圧縮高画質映像の転送、医療画像処理など、様々な分野での応用が期待されています。

具体的には、センシング機器側にFPGAを搭載し、接続先にはRDMA対応のNIC (Network Interface Card) を使用する構成が考えられます。

RDMAのメリット

RDMAの主なメリットは、データ転送時にCPUパワーを消費しないことです。従来のTCP、UDP、RTP、GigE Visionなどのプロトコルでは、NICから受信したパケットをCPUで処理する必要があり、高帯域な転送を行う場合、CPUに大きな負荷がかかっていました。

AIやHPC (High Performance Computing) 分野でRDMA対応NICの入手が容易になったことで、他の分野でもRDMAを活用する環境が整ってきています。

組込み向けIPの特長

Intellectual Highwayが今回リリースしたIPは、組込み用途に特化した特徴を備えています。通常のメモリ経由の転送に加え、ストリーム入出力インターフェースを搭載しており、1マイクロ秒未満の超低遅延な転送を実現します。

また、転送相手とのハンドシェイクを行うコネクションマネージメント機能を、CPUを必要とせずにIP内で完結させることが可能です。これにより、CPU負荷をゼロにし、ストリームインターフェースへの対応、超低遅延という利点を活かした使いやすさを実現しています。

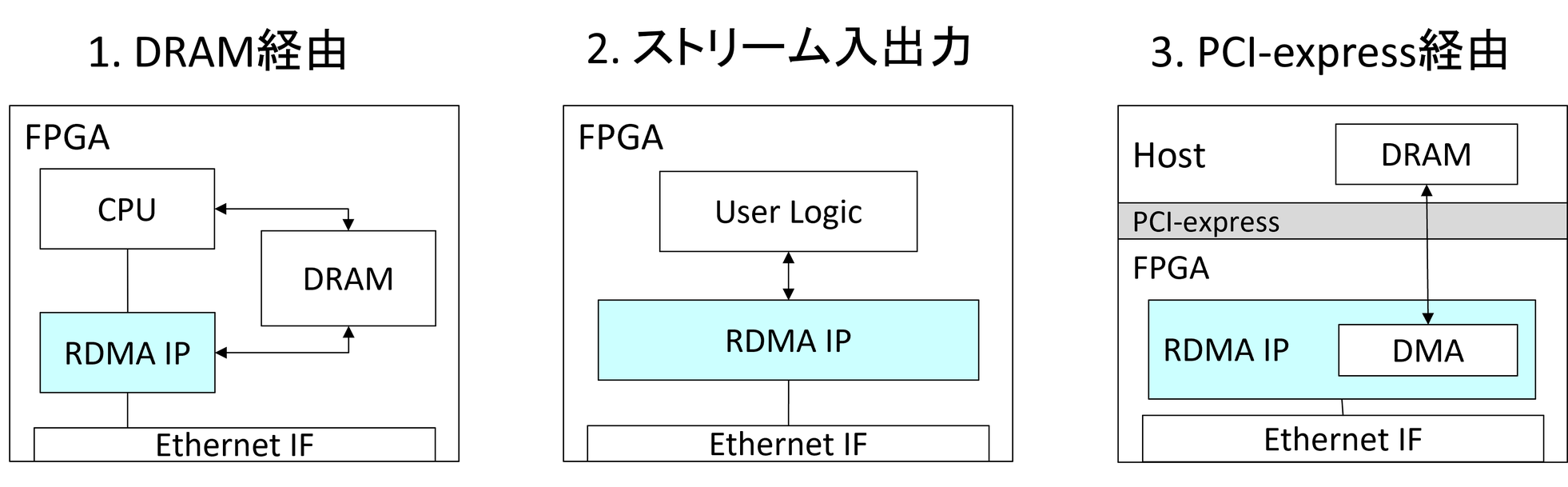

データ入出力形式は、DRAM(メモリ)経由、ストリーム入出力、PCI-express経由の3種類に対応しています。

主な仕様と今後の展開

本IPの主な仕様は以下の通りです。

- プロトコル: RoCEv2, ARP, ICMP (Ping)

- コネクション管理: Communication Management Messageを利用

- コネクションタイプ: Reliable Connection, Unreliable Connection, Unreliable Datagram

- オペレーション: SEND (with Immediate), RDMA WRITE (with Immediate), RDMA READ

- 最大キューペア数: 1 – 4096 (configurable)

- フロー制御: PFC対応, VLAN/PCPタグによる制御

- 輻輳制御: ECN (Explicit Congestion Notification), CNP対応, レート制御可能

- スループット: 100Gbps ワイヤレート (FPGA実装時)

- 対応デバイス (FPGA): Altera Stratix-10シリーズ, Agilexシリーズ, AMD Alveo(UltraScale+)シリーズ, Versalシリーズ

- メモリ: DDR , HBMどちらにも対応

本製品の評価・購入は2025年12月22日より可能です。また、2026年3月末には200Gbps版のリリースが予定されています。

Ms.ガジェット

Ms.ガジェット最後までお読みいただきありがとうございました!

- 本記事の評価は当サイト独自のものです。

- 特段の表示が無い限り、商品の価格や情報などは記事執筆時点での情報です。

- この情報が誤っていても当サイトでは一切の責任を負いかねますのでご了承ください。

- 当サイトに記載された商品・サービス名は各社の商標です。

- 本記事で使用している画像は、メディアユーザーとしてPR TIMESより提供されたプレスリリース素材を利用しています。